# Edge6435/6436 Per-Pin Electronics Companion DAC

# TEST AND MEASUREMENT PRODUCTS

### Description

The Edge6435/6436 is a low-cost, 40-channel, monolithic ATE level DAC solution manufactured in a wide-voltage bi-CMOS process.

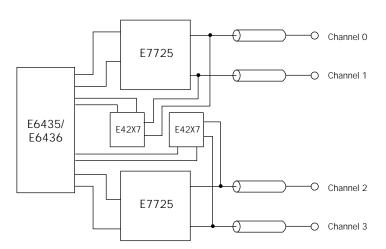

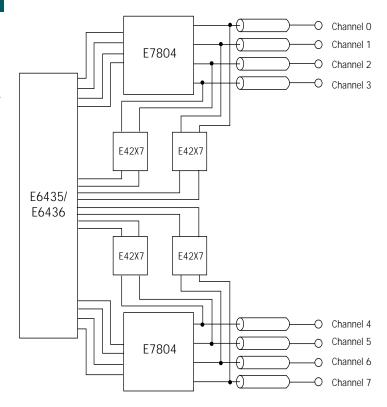

The Edge6435/6436 features independent buffered voltage and current outputs that are serially programmed and can be used to provide all of the reference levels required for up to 8 channels of pin electronics in an ATE system.

#### **Designated Voltage Output DACs**

- Wide Voltage Range (16.75V)

- Adjustable Full-Scale Range

- Adjustable Minimum Offset Voltage

- 13-bit Resolution

- 11-bit Accuracy (E6436)

- 10-bit Accuracy (E6435)

#### Selectable Voltage/Current Output DACs

- Wide Voltage/Current Range (16.75V/2 mA)

- Adjustable Full-Scale Range

- Adjustable Minimum Offset

- Configurable as either Voltage or Current Output

- 13-bit Resolution

- 11-bit Accuracy (E6436)

- 10-bit Accuracy (E6435)

### **Designated Current Output DACs**

- 1.6 mA Range

- Adjustable Full-Scale Range

- 6-bit Resolution

On-chip, digital storage of offset and gain calibration coefficients allow the E6435/6436 output levels to be programmed using "Ideal Code", helping to reduce some of the complexity and time normally associated with programming level DACs in ATE systems.

PINCAST allows the Edge6435/6436 to further reduce this complexity and time by allowing channels across multiple Edge6435/6436 devices to be digitally assigned to up to 8 distinct sets that can be addressed and programmed with a limited number of instructions.

The Edge6435/6436 features 2 ranks of input latches into each DAC, whereby all DAC values may be updated at one time.

For Automated Test Equipment, the Edge6435/6436 can support Pin Electronics and Parametric Measurement Units whose outputs are in the range of -3.25V to +13V, and Driver Super Voltages to +13V after calibration. It provides 10 or 5 per pin levels for 4 or 8 channels respectively. The Edge6435/6436 is designed such that DACs may be shared for various levels whereby minimizing the total number of DACs required in a specific application.

#### Features

- 40 DACs Partitioned into 4 Groups for 4 or 8 Pin Channels

- Wide Voltage Output Range (16.75V Range)

- 24 Voltage DACs per Package

- 8 Voltage / Current DACs per Package

- 8 Current DACs per Package

- Adjustable Full-Scale Range and Offset per Group

- DUT GND or Analog GND Reference per Group

- Self-Calibrating DACs via Internal Offset, Gain Registers

- Two Offset, Gain Registers to Support Sharing of DACs

- DAC Programming per Channel or Set of Channels

- Readback of DAC Input Data and Output Value

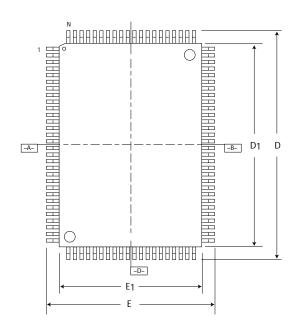

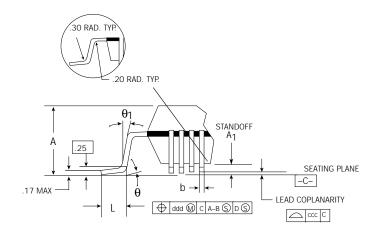

- Small 100-Pin MQFP Package

- Low-Cost, Highly Integrated Multi-DAC Solution

### **Applications**

- Automated Test Equipment (ATE)

- Cost Sensitive applications requiring multiple programmable voltage and currents

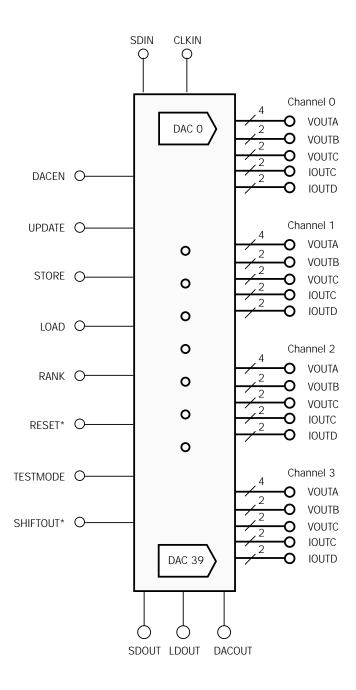

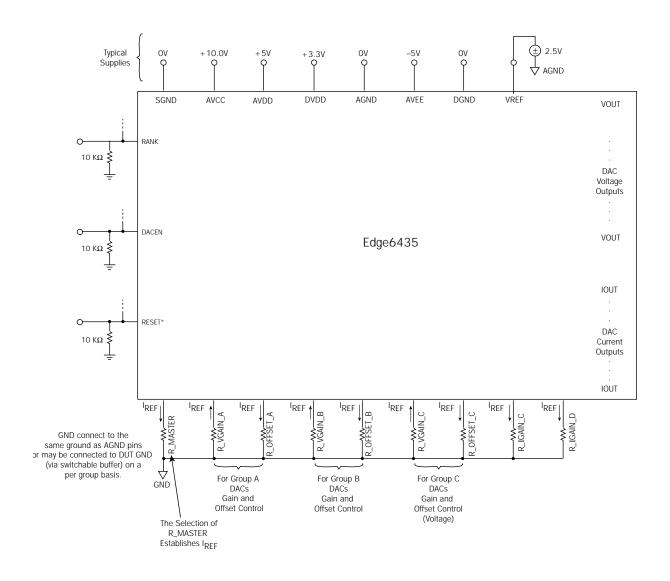

# Functional Block Diagram

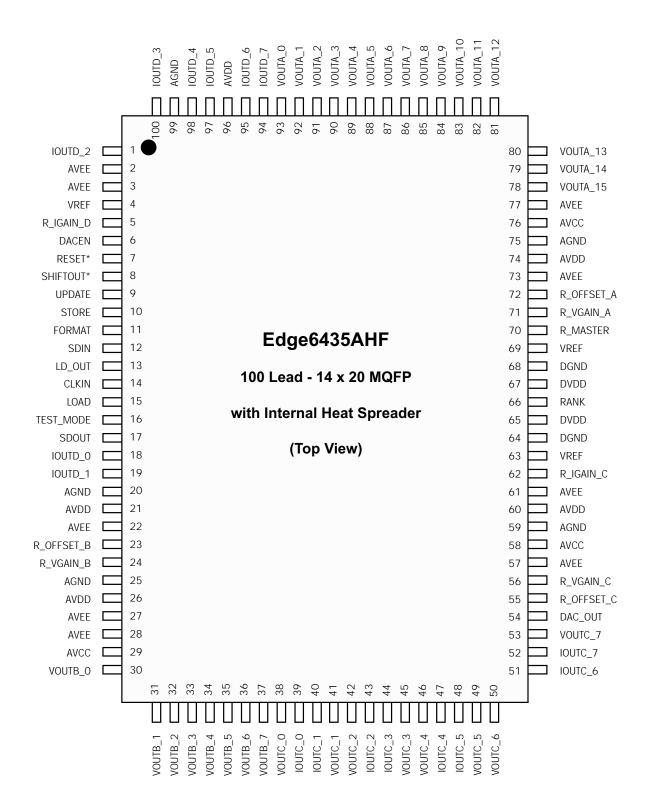

# PIN Description

| Pin Name         | Pin #                               | Description                                                                                                                                                         |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supplies   |                                     |                                                                                                                                                                     |

| AVCC             | 29, 58, 76                          | Positive Analog Supply Pins (Output Buffer Supply)                                                                                                                  |

| AVEE             | 2, 3, 22, 27, 28,<br>57, 61, 73, 77 | Negative Analog Supply Pins                                                                                                                                         |

| AVDD             | 21, 26, 60, 74, 96                  | Positive Analog Supply Pins (Core DAC Supply)                                                                                                                       |

| AGND             | 20, 25, 59, 75, 99                  | Analog Supply Ground Pins                                                                                                                                           |

| DVDD             | 65, 67                              | Digital Supply Input Pins                                                                                                                                           |

| DGND             | 64, 68                              | Digital Supply Ground Pins                                                                                                                                          |

| VREF             | 4, 63, 69                           | Reference Voltage Input                                                                                                                                             |

| Digital I/O Pins |                                     |                                                                                                                                                                     |

| CLKIN            | 14                                  | Clock input pin.                                                                                                                                                    |

| SDIN             | 12                                  | Serial data input pin that is used to read 24-bit words into the E6435 input shift register.                                                                        |

| LOAD             | 15                                  | Digital input pin that triggers the transfer of data from the serial data input shift register to the central DAC register at up to 33 MHz.                         |

| STORE            | 10                                  | Digital input pin that is used to update the rank A latches.                                                                                                        |

| UPDATE           | 9                                   | Digital input pin that is used to update the rank B latches.                                                                                                        |

| RANK             | 66                                  | Digital input pin that selects either data in the rank A or rank B latches as the DAC input.                                                                        |

| FORMAT           | 11                                  | Digital input pin used to select between "4-channel" or "8-channel" decoding schemes.                                                                               |

| RESET*           | 7                                   | Digital input pin that is used to initialize the E6435 by placing it into a known state.                                                                            |

| DACEN            | 6                                   | Digital input pin that is used to set all DAC outputs ~OV (Voltage output DACs) or ~OmA (Current output DACs).                                                      |

| SDOUT            | 17                                  | Serial data output pin.                                                                                                                                             |

| Diagnostic Pins  | •                                   |                                                                                                                                                                     |

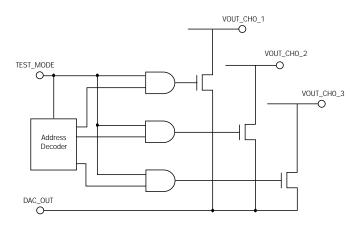

| TEST_MODE        | 16                                  | Digital input pin that is used to enable/disable the DAC_OUT and LD_OUT functions.                                                                                  |

| DAC_OUT          | 54                                  | High impedance analog voltage output pin that displays the output level of a selected DAC (used for system level diagnostics) when enabled using the TEST_MODE pin. |

| SHIFTOUT*        | 8                                   | Digital input pin that is used to begin the transmission of serial data through the LD_OUT pin.                                                                     |

| LD_OUT           | 13                                  | Serial data output pin used to display the binary value stored in a selected rank A or rank B latch.                                                                |

# PIN Description (continued)

| Pin Name                                                                                                                                       | Pin #                                                                                  | Description                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------|

| 13-Bit Voltage Outpu                                                                                                                           | t DACs                                                                                 |                                  |

| VOUTA_O VOUTA_1 VOUTA_2 VOUTA_3 VOUTA_4 VOUTA_5 VOUTA_6 VOUTA_7 VOUTA_8 VOUTA_9 VOUTA_10 VOUTA_11 VOUTA_11 VOUTA_12 VOUTA_13 VOUTA_14 VOUTA_15 | 93<br>92<br>91<br>90<br>89<br>88<br>87<br>86<br>85<br>84<br>83<br>82<br>81<br>80<br>79 | Group A Voltage DAC Output Pins. |

| VOUTB_O VOUTB_1 VOUTB_2 VOUTB_3 VOUTB_4 VOUTB_5 VOUTB_6 VOUTB_7                                                                                | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37                                           | Group B Voltage DAC Output Pins. |

| 13_Bit Selectable Vo                                                                                                                           | Itage/Current Output                                                                   | t DACs                           |

| VOUTC_0<br>VOUTC_1<br>VOUTC_2<br>VOUTC_3<br>VOUTC_4<br>VOUTC_5<br>VOUTC_6<br>VOUTC_7                                                           | 38<br>41<br>42<br>45<br>46<br>49<br>50<br>53                                           | Group C Voltage DAC Output Pins. |

| IOUTC_O IOUTC_1 IOUTC_2 IOUTC_3 IOUTC_4 IOUTC_5 IOUTC_6 IOUTC_7                                                                                | 39<br>40<br>43<br>44<br>47<br>48<br>51<br>52                                           | Group C Current DAC Output Pins. |

| 6-Bit Current Output                                                                                                                           | DACs                                                                                   |                                  |

| IOUTD_O IOUTD_1 IOUTD_2 IOUTD_3 IOUTD_4 IOUTD_5 IOUTD_6 IOUTD_7                                                                                | 18<br>19<br>1<br>100<br>98<br>97<br>95<br>94                                           | Group D Current DAC Output Pins. |

# PIN Description (continued)

| Pin Name             | Pin # | Description                                                                                                                                                              |

|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Resistor Connections |       | •                                                                                                                                                                        |

| R_MASTER             | 70    | External resistor connection used in combination with R_VGAIN_A, R_VGAIN_B, and R_VGAIN_C to set the maximum output range for the Group A, B, and C voltage output DACs. |

| R_VGAIN_A            | 71    | External Resistor connection used in combination with R_MASTER to set the maximum range for the group A voltage DAC outputs.                                             |

| R_VGAIN_B            | 24    | External Resistor connection used in combination with R_MASTER to set the maximum range for the group B voltage DAC outputs.                                             |

| R_VGAIN_C            | 56    | External Resistor connection used in combination with R_MASTER to set the maximum range for the group C voltage DAC outputs.                                             |

| R_OFFSET_A           | 72    | External resistor connection used to set the base offset voltage for group A voltage DAC outputs.                                                                        |

| R_OFFSET_B           | 23    | External resistor connection used to set the base offset voltage for group B voltage DAC outputs.                                                                        |

| R_OFFSET_C           | 55    | External resistor connection used to set the base offset voltage for group C voltage DAC outputs.                                                                        |

| R_IGAIN_C            | 62    | External resistor connection used to set the maximum range for the group C current DAC outputs.                                                                          |

| R_IGAIN_D            | 5     | External resistor connection used to set the maximum range for the group D current DAC outputs.                                                                          |

PIN Description (continued)

### Circuit Description

#### **Chip Overview**

The Edge6435/6436 provides 40 output levels. These outputs can easily be configured to generate the specific analog voltage and current requirements for 4 or 8 channels of ATE pin electronics including:

- 3 level driver

- Window comparator

- Active load

- Per pin PMU or PTU

without requiring any scaling or shifting via external components.

Selection of 4 or 8 channel format is via the FORMAT input.

Programming of the chip is done using a 6 wire digital interface comprised of:

- Serial Data In

- Clock In

- Load

### **Grouping of DACs**

DACs are separated into 4 or 8 channels of 4 distinct functional groups. Groups are defined by:

- Type (voltage or current output)

- Resolution (# of bits)

- Output range

- Output compliance.

Table 1 defines the DACs on a per group and channel basis.

Group C DACs have both voltage and current output pins.

Group C DACs can be individually configured via the serial interface to be either a voltage or current DAC (but not both at the same time).

Tables 3 and 4 identify the code needed to configure Group C DACs. Please note that 24 clock cycles are required to load the configuration code for each channel.

| Attribute                                           |             | Group<br>A                | Group<br>B                | Group<br>C                                             | Group<br>D    |

|-----------------------------------------------------|-------------|---------------------------|---------------------------|--------------------------------------------------------|---------------|

| Total # of DACs in Croup                            | 4 CH Format | 4 per channel             | 2 per channel             | 2 per channel                                          | 2 per channel |

| Total # of DACs in Group                            | 8 CH Format | 2 per channel             | 1 per channel             | 1 per channel                                          | 1 per channel |

| Туре                                                |             | V                         | V                         | V/I                                                    | I             |

| Resolution (# of bits)                              |             | 13                        | 13                        | 13                                                     | 6             |

| Output Range:  Max DAC Range (Note 1)  Offset Range |             | 16.75V<br>-3.5V to -0.75V | 16.75V<br>-3.5V to -0.75V | 16.75V<br>-3.5V to -0.75V<br>or<br>2.05 mA<br>(Note 2) | 1.6 mA        |

| Adjustable Output Offset                            |             | yes                       | yes                       | yes for Vout<br>no for lout                            | no            |

| Compliance                                          |             | ±200 μA                   | ±200 μA                   | ±200 μA(V)<br>-0.2 to +3V(I)                           | -0.2 to +3V   |

Note 1: The max DAC range is achieved through specific AVCC, AVEE, and Gain resistor settings. See the equations in the "DAC Voltage Output Overview", "DAC Current Output Overview", and specifications for details.

*Note 2:* Group C has both voltage and current outputs.

# Circuit Description (continued)

#### Voltage Outputs DACs (Groups A, B, C)

The output voltage of each E6435/6436  $V_{OUT}$  DAC is a function of external resistor values (R\_MASTER, R\_VGAIN and R\_OFFSET), a reference voltage level ( $V_{REF}$ ), contents of digital offset and gain registers, and the programmed input code (DATA). The general equation that describes the output voltage as a function of these variables is presented below as Equation 1:

$$V_{OUT\_[A:C]} = \left(8 * V_{REF} * \frac{R_VGAIN\_[A:C]}{R_MASTER} * \frac{CODE}{8192}\right) + V_{OFFSET\_[A:C]}$$

#### Equation 1.

#### where:

Vout[A:C] is the output voltage of a Group A, B, or C Voltage DAC.

VREF is an externally applied 2.5V reference voltage

R\_VGAIN[A:C] is the value of an external resistor used to set the range for Group A, B, or C DACs

R\_MASTER is the value of an external resistor that sets the bias point/range for the voltage DACs

CODE is the base-10 value of the binary code (DATA) loaded into the DAC shift register (see Figures 4 and 5) after it has been modified by the contents of the digitally programmable offset and gain calibration registers as shown in Figure 2.

VOFFSET[A:C] is the raw DAC offset voltage that is programmed using an external resistor per group, R\_OFFSET[A:C] as follows:

$$V_{OFFSET\_[A:C]} = -V_{REF} \left( \frac{R_OFFSET\_[A:C]}{R_MASTER} \right)$$

#### Equation 2.

As can be seen from Equation 1, the accuracy of the DAC output voltage after calibration is dependent upon the temperature coefficients of V<sub>REF</sub> and the external resistors.

#### Minimum / Maximum Output Voltages

See Table 2 for the minimum and maximum possible voltages of a voltage output, where:

V<sub>OFFSET[A:C]</sub> is defined in equation 2, and

$$V_{MAX\_[A:C]} = \left(8 * V_{REF} * \frac{R\_VGAIN\_[A:C]}{R\_MASTER} * \frac{8191}{8192}\right) + V_{OFFSET\_[A:C]}$$

Equation 3.

#### Resolution

The resolution of the DACs in Groups A, B and C is:

$$V_{RANGE} [A:C] / (2^{13} - 1)$$

where V<sub>RANGE</sub> [A:C] is defined in Equation 4.

#### Range

The range of the DACs in Groups A, B and C is:

$$V_{RANGE\_[A:C]} = 8 * V_{REF} * \frac{R_VGAIN\_[A:C]}{R_MASTER} * \frac{8191}{8192}$$

#### Equation 4.

#### External Resistors

Typically computed for R\_MASTER =  $100k\Omega$ .

| DAC Setting<br>MSB LSB | V <sub>OUT_[A:C]</sub> (V) |

|------------------------|----------------------------|

| 0000Н                  | V <sub>OFFSET_[A:C]</sub>  |

| 1FFFH                  | V <sub>MAX_[A:C]</sub>     |

Table 2. Minimum/Maximum Output Voltages

# Circuit Description (continued)

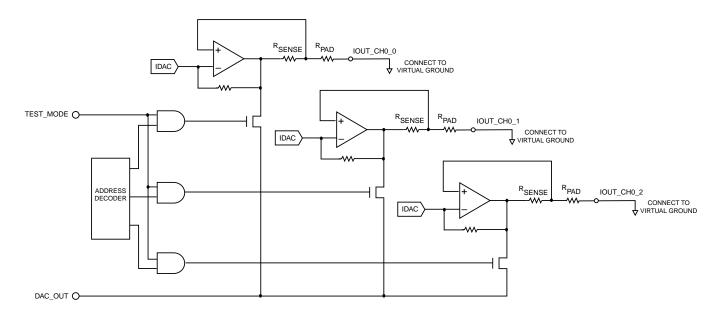

### Current Output DACs (Groups C, D)

### Group C DACs

The output current of each Group C Current DAC is a function of an external resistor value (R\_IGAIN\_C), a reference voltage level (VREF), contents of digital offset and gain registers, and the input code (DATA). The general equation that describes the output current as a function of these variables is presented below as Equation 5:

$$I_{OUT\_C} = \frac{CODE}{8192} * \frac{50 \times V_{REF}}{R \text{ IGAIN C}}$$

#### Equation 5.

where:

$\ensuremath{\mathsf{IOUT\_C}}$  is the output current of the Group C Current DAC

VREF is an externally applied 2.5V reference voltage

R\_IGAIN\_C is the value of an external resistor that sets the output current range for Group C DACs  $(60.97 \text{K}\Omega \leq \text{R_IGAIN_C} \leq 250 \text{K}\Omega)$

CODE is the base-10 value of the binary code (DATA) loaded into the DAC shift register (see Figures 4 and 5) after it has been modified by the contents of the digitally programmable offset and gain calibraiotn registers as shown in Figure 2.

#### **Group D DACs**

The output current of each group D DAC is a function of an external resistor value (R\_IGAIN\_D), a reference voltage level (VREF) and the input code (DATA). The general equation that describes the output current as a function of these variables is presented below as Equation 6:

$$I_{OUT\_D} = \frac{DATA}{64} * \frac{50 \times V_{REF}}{R \text{ IGAIN D}}$$

#### Equation 6.

where:

$I_{OUT\_D}$  is the output current of the Group D DAC

VREF is an externally applied 2.5V reference voltage

R\_IGAIN\_D is the value of an external resistor that sets the output current range for Group D DACs  $(78.12K\Omega \le R \text{ IGAIN D} \le 156.25K\Omega)$

DATA is the base-10 value of the binary code loaded into the DAC shift register (see Figures 4 and 5).

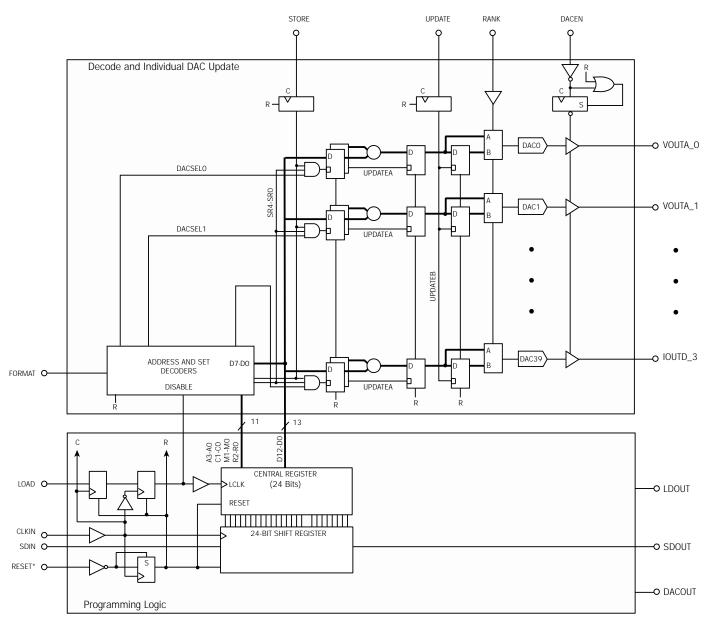

#### **Functional Description**

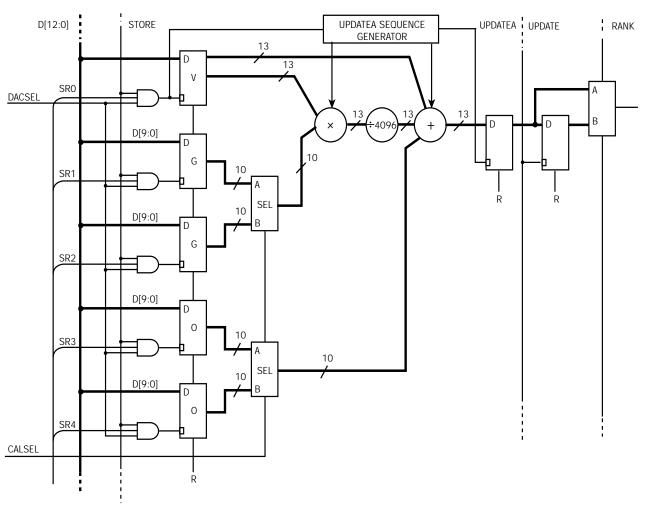

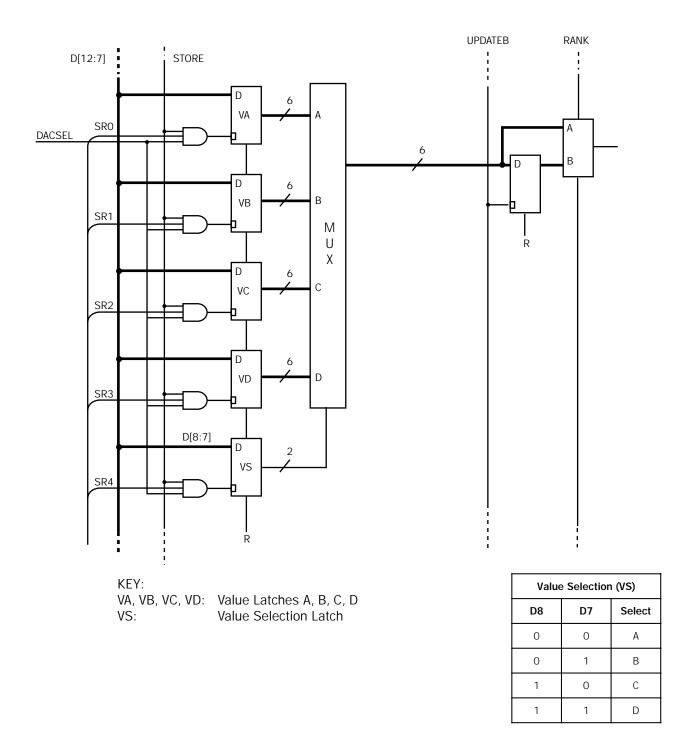

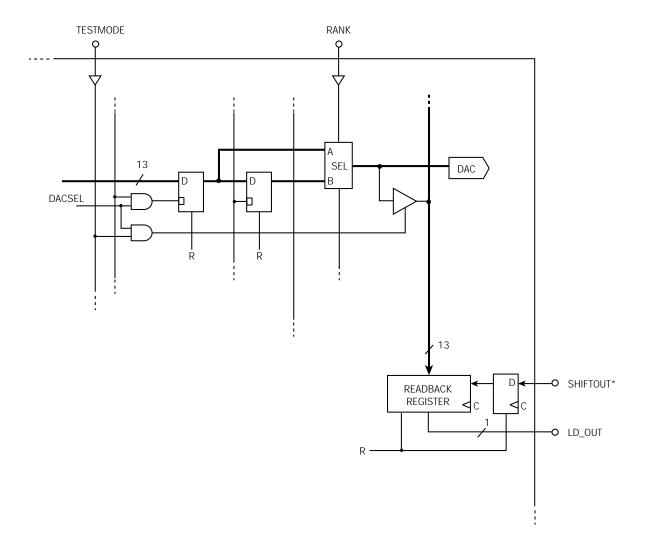

Figure 1 provides a Functional Block Diagram. Figures 2 and 3 show details of the data latches and logic for the DACs. The Edge6435/6436 features a serial data input to program a channel or set of channel's DACs and functions. The Edge6435/6436 also features self-calibrating DAC outputs via internal offset and gain registers (Figure 2).

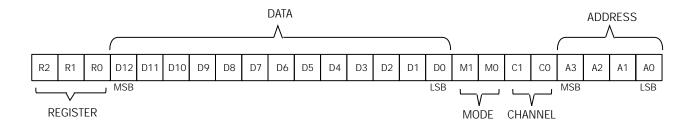

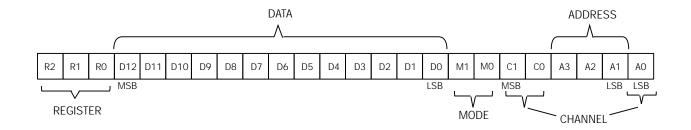

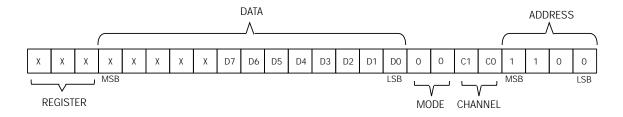

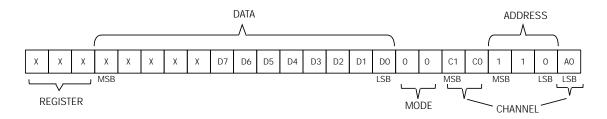

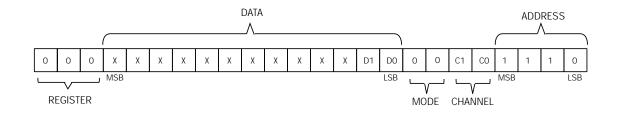

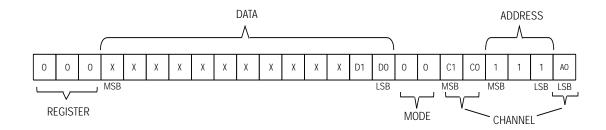

Figures 4 and 5 show the format of the Serial Input Data for 4 pin channel and 8 pin channel formats.

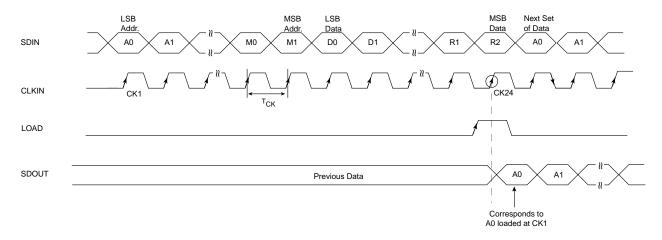

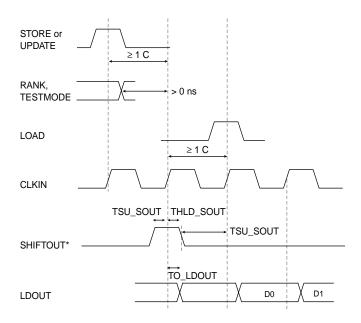

Figure 6 shows the Serial Data Programming Sequence

Tables 3 and 4 provide the Address Maps for 4 pin channel and 8 pin channel formats.

#### **FORMAT**

FORMAT Low selects the 4 pin channel format. FORMAT High selects the 8 pin channel format.

# Circuit Description (continued)

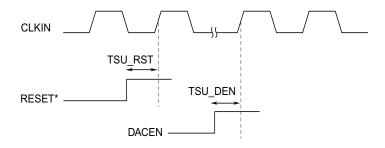

#### **RESET\***

RESET\* low resets the input shift register (no CLKIN required), the central register, and input registers. With RESET\* high, the following leading edge of CLKIN will cause reset condition to be removed (see Figure 21). Two clock cycles are required after RESET\* is set to logic "high" for the DAC outputs to be enabled.

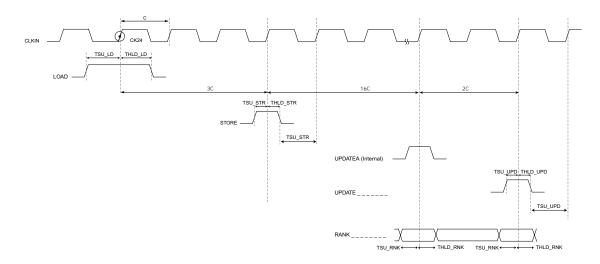

### **Programming Sequence**

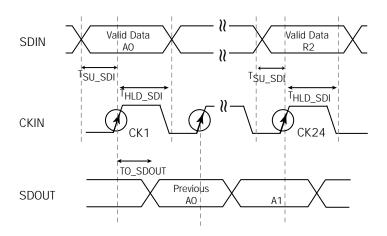

The DACs are programmed serially (see Figures 1 and 6). On each rising edge of CLKIN, SDIN is loaded into a shift register. It requires 24 Clocks to fully load the shift register.

#### LOAD

Following the serial input of a new DAC value, then LOAD high for the leading edge of CLKIN loads the new DAC value and its address into the Central Register. Following the loading of the Central Register, LOAD needs to go low followed by a leading edge of CLKIN so as to enable the address decoder (see Figure 6).

#### **STORE**

Following the LOAD of the Central Register and the enabling of the address docoder, the channel or set of channels addressed DACs input register or channel function is "stored" by a CLKIN with STORE high. Only upon the STORE of a DAC or set of DAC's "value latch" (Figure 2) does the Edge6435/6436 compute the input to DAC's Latch A (of Rank A). There needs to be at least one clock edge after LOAD is set to logic "low" before STORE is set to logic "high" (see Figure 21).

#### **UPDATE**

Following the STORE of multiple DAC values into Rank A DAC latches, Rank B latches may be updated in parallel with the values of their Rank A DAC latches by a CLKIN with UPDATE high. There must be at least 16 clock cycles between when STORE is set to logic "low" and UPDATE is latched to logic "high" in order to latch the latest data (see Figure 21).

#### **RANK Selection**

Referring to Figures 1, 2 and 3:

RANK low selects Rank A latches to the DACs (no CLKIN required).

RANK high selects Rank B latches to the DACs (no CLKIN required).

#### **DACEN**

DACEN low forces all DAC voltage outputs to ~0V and all current outputs to ~0 mA (no CLKIN required). With DACEN high, then a following leading edge of CLKIN will cause DACs to be enabled (see Figure 23).

#### **TEST MODE/SHIFTOUT\***

TEST\_MODE is used to enable the LDOUT and DACOUT channels. Once enabled (TESTMODE = 1), SHIFTOUT\* can be used to begin transmission of serial data through the LDOUT pin, or DAC outputs can be monitored at the DACOUT pin (see Figure 24) (TEST\_MODE functionality does not depend on CLKIN)).

When addressing DAC channels that have been assigned to a PinCast "set", TEST-MODE is internally disabled in order to prevent multiple DAC outputs from being connected in parallel and possibly damaging the E6435/6436.

# Circuit Description (continued)

### **Serial Programming**

The Edge6435/6436 is programmed with 24-bit serial data (Figure 6) in either a 4 channel (Figure 4) or 8 Channel (Figure 5) format.

Following the input of serial data, it is loaded into a central register by LOAD (Figure 1). The central register's contents are stored in the "addressed" latch by the STORE input. Tables 3 and 4 show the "Address Maps" for the 4 and 8 channel formats.

Referring to Table 3 for 4 channel format, a channel's DACs Set Register or Function may be addressed and the "stored" value changed. For each DAC, there are associated multiple latches (Figures 2 and 3). For the 13-bit DACs (Figure 2) the DAC's output is a function of the contents of its value, gain and offset latches. The Edge6435/6436 features two gain and offset latches per DAC whereby a DAC's output may be shared. For example, in ATE a DAC's value may be shared between a pin driver's high level and a pin's parametric unit's high limit level, where each application requires different offset and gain factors to calibrate each path correctly. Gains and offsets are computed externally to the Edge6435/6436 in the process of pin channel level calibration in the ATE. Gains and offsets are stored in the Edge6435/6436 in the same manner as other latches. Selection of what is stored is determined by the "register selection" bits in the 24-bit input data (Figures 2 and 4). Upon storing a 13-bit DAC's Value, the resultant DAC's ((Value x Gain) + Offset + 4096

Value) is updated by UPDATEA (Figure 2) into the DAC's output latch of RANKA. The contents of all RANKA latches may be transferred to RANKB latches, in parallel, across multiple Edge6435/6436's by the UPDATE input into the Edge6435/6436. The RANK input into the Edge6435/6436 selects either RANKA or RANKB latches for all DACs.

For the 6-bit DACs (Figure 3) the DAC's output is selected from four "value latches".

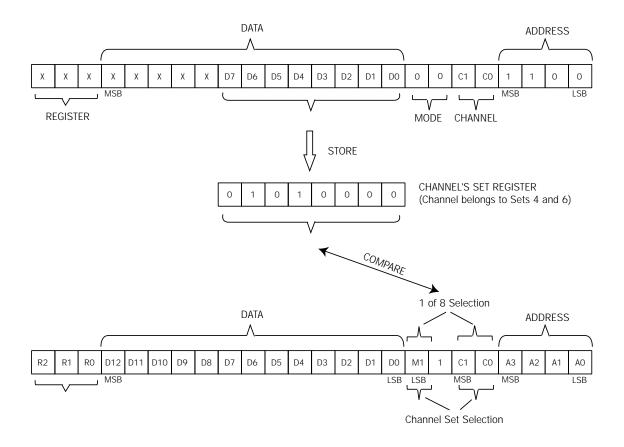

Referring to Table 3, a channels Set Register may also be programmed. This is an independent 8-bit register per channel which determines the "sets" to which the channel belongs. Figure 7 shows details of programming a channel's Set Register, which is stored in the Edge6435/6436 by the STORE input. A channel may

belong to none, one, or any combination of up to 8 distinct sets. The address maps show that a channel's DAC (or Function) may be addressed individually, or a DAC (or Function) of multiple channels belonging to the same set may be programmed in parallel. Figure 11 shows an example of addressing channels by sets.

Referring to Table 3, a Channel's function is programmed as indicated in Figure 9 (offset and gain selection as well as Group C DAC V/I output selection, see below).

Channel's Functions (for 13 bit DACs only), with R2 = R1 = R0 = 0, then:

D0 = 0: Selects 1st Offset/Gain Registers

D0 = 1: Selects 2nd Offset/Gain Registers

D1 = 0: Selects Voltage Output on Group C DACs

D1 = 1: Selects Current Output on Group C DACs

Referring to Table 4 for 8 channel format, and Figures 2, 3, 5, 8 and 10, a channel's DACs, Set Registers and Function, etc. are programmed and operate similar to the 4 channel format described above.

NOTE: The STORE of a DAC's offset or gain does not result in a DAC output change. Only upon the STORE of a DAC or set of DAC's "value" does the Edge6435/6436 compute the input to DAC's "A" latches.

In a tester having multiple Edge6435/6436s, DACs or channel functions may be programmed individually or as a set (1 of 8) of channels across all channels. If multiple E6435/6436s are programmed in parallel, individual DAC or Function programming requires the STORE input to the associated Edge6435/6436 to be applied where all STORE inputs to other Edge6435/6436s are to be inhibited (externally). Programming a DAC or Function of a Set of Channels requires STORE input to be applied to all Edge6435/6436s. Edge6435/6436's DACs may be "updated" in parallel following the programming of DACs as individual DACs or sets of DACs.

# Circuit Description (continued)

NOTE: VOUT, IOUT names shown for 4 Channel Format.

NOTE: Not shown is the function of the Latched Data Readback (via LDOUT) and the DAC Value Readback (via DACOUT). Details of the 'Store' Latches are shown on the following pages.

Figure 1. DAC Functional Block Diagram

# Circuit Description (continued)

KEY:

V: Value Latch that contains DATA programmed to a DAC (see Figures 4 & 5).

- O: Offset Latches that are used to store offset calibration coefficients (two offset latches per DAC allow the DAC to be shared in a system).

- G: Gain Latches that are used to store gain calibration coefficients (two gain latches per DAC allow the DAC to be shared in a system).

NOTE: CALSEL common to all DACs assigned to a Channel

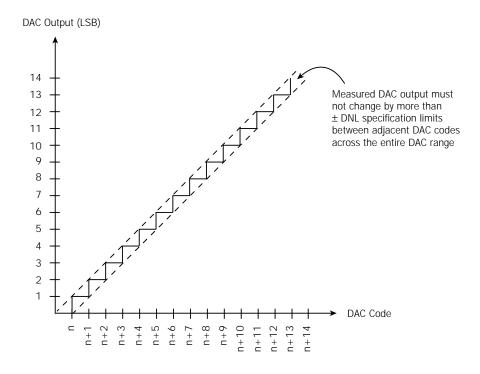

DAC Output (CODE):

$$CODE = \frac{V * (G + 4096)}{4096} + 0$$

| Function          | F  | Register | Select | ion    |

|-------------------|----|----------|--------|--------|

| runction          | R2 | R1       | R0     | Select |

| DAC Data          | 0  | 0        | 0      | SR0    |

| Gain Register A   | 0  | 0        | 1      | SR1    |

| Gain Register B   | 0  | 1        | 0      | SR2    |

| Offset Register A | 0  | 1        | 1      | SR3    |

| Offset Register B | 1  | 0        | 0      | SR4    |

Figure 2. Details of DAC Data Latches for 13 Bit DACs (Groups A, B, and C)

Figure 3. Details of DAC Data Latches for 6 Bit DACs (Group D)

Figure 4. Format of Address and Data in Shift Register (4 Channel Format)

Figure 5. Format of Address and Data in Shift Register (8 Channel Format)

Figure 6. Serial Data Programming Sequence

Figure 7. Format of Address and Data for Programming to SET REGISTER (4 Channel Format)

Figure 8. Format of Address and Data for Programming to SET REGISTER (8 Channel Format)

Figure 9. Format of Address and Data for Programming a Channel's Function (4 Channel Format)

Figure 10. Format of Address and Data for Programming a Channel's Function (8 Channel Format)

# Circuit Description (continued)

If Set 4 is selected, then channel's DAC value or Function will be 'stored'. If Set 3 is selected, then the channel will not be 'addressed'.

Figure 11. Example of Channel's Set Selection (4 Channel Format)

# Circuit Description (continued)

|                   |              | Bit #                                                                                               |                       | 23          |             |        |             | 19-16       | 15-12                | 11          | 10          | 9           | 8      | 7               | 6        | 5        | 4         | 3   | 2           | 1           | 0          |                                           |

|-------------------|--------------|-----------------------------------------------------------------------------------------------------|-----------------------|-------------|-------------|--------|-------------|-------------|----------------------|-------------|-------------|-------------|--------|-----------------|----------|----------|-----------|-----|-------------|-------------|------------|-------------------------------------------|

| ECD:              | 4AT - A      | Hex Multiplier                                                                                      |                       |             | 0x10        |        |             | 0x01 0000   |                      | _           |             | 100         | -      | _               |          | 010      |           | _   |             | 0001        |            | May Outt D                                |

| FORM              | MAT = 0      | Binary Position                                                                                     | DAC Output            | 8<br>Rea    | 4<br>ister  | 2      | 1           | 8 - 1       | 8 - 1<br><b>Data</b> | 8           | 4           | 2           | 1      | 8<br><b>M</b> d | 4<br>ode | 2<br>Cha | 1<br>nnel | 8   | 4<br>Ad     | 2<br>dress  | <u>  1</u> | Max Output Range                          |

|                   |              | ltem                                                                                                | Pin Name              | R2          | R1          | R0     | D12         | D11 - D8    | D7 - D4              | D3          | D2          | D1          | D0     | M1              | M0       | C1       | CO        | А3  | _           | _           | Α0         |                                           |

|                   |              |                                                                                                     | VOUTA_0               | Χ           | Χ           | Х      | Χ           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 0         | 0   | 0           | 0           | 0          |                                           |

|                   |              | Group A 13-bit V                                                                                    | VOUTA_1               | Х           | Х           | Х      | Х           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         | 0   | 0           | 0           | 1          | -3.5V to +13.75V                          |

|                   |              | ·                                                                                                   | VOUTA_2<br>VOUTA_3    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         | 0   | 0           | 1           | 1          | (16.75V Max Swing)                        |

|                   |              | Reserved                                                                                            | N/A                   | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         |     |             | - 01        |            | N/A                                       |

|                   | ı            | Group B 13-bit V                                                                                    | VOUTB_0               | Х           | Χ           | Х      | Х           | Х           | Х                    | Х           | Χ           | Χ           | Х      | 0               | 0        | 0        | 0         | 0   | 1           | 1           | 0          | -3.5V to +13.75V                          |

|                   |              | Cloup B 10 Bit V                                                                                    | VOUTB_1               | Х           | X           | X      | Х           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         | 0   | 1           | 1           | 1          | (16.75V Max Swing)                        |

|                   | 0            | Group C 13-bit V/I                                                                                  | VOUTC_0, IOUTC_0      | Х           | Х           | Х      | Х           | Х           | Х                    | Χ           | Х           | Х           | Х      | 0               | 0        | 0        | 0         | 1   | 0           | 0           | 0          | V: -3.5V to +13.75V<br>(16.75V Max Swing) |

|                   | CHANNEL      |                                                                                                     | VOUTC_1, IOUTC_1      | Х           | Х           | Х      | Х           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 0         | 1   | 0           | 0           | 1          | I: 0.5mA to 2.05mA                        |

|                   | AN           | Group D 6-bit I (Note 1)                                                                            | IOUTD_0               | Χ           | Χ           | Χ      | Χ           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 0         | 1   | 0           | 1           | 0          | 0.8mA to 1.6mA                            |

|                   | ರ            | PINCAST Register 0                                                                                  | IOUTD_1<br>N/A        | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         | 1   | 1           | 0           | 0          | N/A                                       |

|                   | l            | Reserved                                                                                            | N/A                   | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 0         | 1   | 1           | 0           | 1          | N/A                                       |

|                   |              | Select Rank 1 Calibration Registers                                                                 |                       | 0           | 0           | 0      | Χ           | Х           | Х                    | Χ           | Χ           | Х           | 0      | 0               | 0        | 0        | 0         | 1   | 1           | 1           | 0          |                                           |

|                   |              | Select Rank 2 Calibration Registers                                                                 | N/A                   | 0           | 0           | 0      | X           | X           | X                    | X           | X           | 0<br>0      | 1<br>X | 0               | 0        | 0        | 0         | 1   | 1           | 1           | 0          | N/A                                       |

|                   | l            | Configure Group C DACs as Vout Configure Group C DACs as lout                                       |                       | 0           | 0           | 0      | X           | X           | X                    | X           | X           | 1           | X      | 0               | 0        | 0        | 0         | 1   | 1           | 1           | 0          |                                           |

|                   |              | Reserved                                                                                            | N/A                   | Χ           | Χ           | Х      | Χ           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 0         | 1   | 1           | 1           | 1          | N/A                                       |

| [                 |              |                                                                                                     | VOUTA_4               | Х           | Х           | Х      | Х           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 1         | 0   | 0           | 0           | 0          |                                           |

|                   |              | Group A 13-bit V                                                                                    | VOUTA_5<br>VOUTA 6    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 0   | 0           | 1           | 0          | -3.5V to +13.75V<br>(16.75V Max Swing)    |

|                   |              |                                                                                                     | VOUTA_6<br>VOUTA_7    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 0   | 0           | 1           | 1          | (10.75V IVIAX SWIFIG)                     |

|                   |              | Reserved                                                                                            | N/A                   | Χ           | Χ           | Χ      | Χ           | Х           | Х                    | Χ           | Χ           | Х           | Х      | 0               | 0        | 0        | 1         |     |             | - 01        |            | N/A                                       |

|                   |              | Group B 13-bit V                                                                                    | VOUTB_2<br>VOUTB_3    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 0   | 1           | 1           | 1          | -3.5V to +13.75V<br>(16.75V Max Swing)    |

|                   | <del>-</del> |                                                                                                     | VOUTC 2, IOUTC 2      | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 1   | 0           | 0           | 0          | V: -3.5V to +13.75V                       |

|                   | CHANNEL 1    | Group C 13-bit V/I                                                                                  | VOUTC_3, IOUTC_3      | Х           | Х           | Х      | Х           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 0        | 1         | 1   | 0           | 0           | 1          | (16.75V Max Swing)                        |

|                   | AN           |                                                                                                     |                       |             |             | ^      |             |             |                      |             |             |             |        |                 |          |          |           |     |             |             | <u> </u>   | I: 0.5mA to 2.05mA                        |

|                   | 끙            | Group D 6-bit I (Note 1)                                                                            | IOUTD_2               | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 1   | 0           | 1           | 1          | 0.8mA to 1.6mA                            |

|                   | ŀ            | PINCAST Register 1                                                                                  | IOUTD_3<br>N/A        | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 0        | 1         | 1   | 1           | 0           | 0          | N/A                                       |

| , <u>,</u>        |              | Reserved                                                                                            | N/A                   | Χ           | Χ           | Х      | Х           | Х           | Х                    | Χ           | Χ           | Χ           | Х      | 0               | 0        | 0        | 1         | 1   | 1           | 0           | 1          | N/A                                       |

| NO I              |              | Select Rank 1 Calibration Registers                                                                 |                       | 0           | 0           | 0      | Х           | X           | X                    | X           | X           | X           | 0      | 0               | 0        | 0        | 1         | 1   | 1           | 1           | 0          |                                           |

| CI                | ŀ            | Select Rank 2 Calibration Registers Configure Group C DACs as Vout                                  | N/A                   | 0           | 0           | 0      | X           | X           | X                    | X           | X           | 0<br>0      | 1<br>X | 0               | 0        | 0        | 1         | 1   | 1           | 1           | 0          | N/A                                       |

| l i               | l            | Configure Group C DACs as lout                                                                      |                       | 0           | 0           | 0      | Х           | X           | X                    | Х           | X           | 1           | X      | 0               | 0        | 0        | 1         | 1   | 1           | 1           | 0          |                                           |

| CHANNEL FUNCTIONS |              | Reserved                                                                                            | N/A                   | Χ           | Χ           | Χ      | Χ           | Х           | Х                    | Χ           | Χ           | Х           | Х      | 0               | 0        | 0        | 1         | 1   | 1           | 1           | 1          | N/A                                       |

| N                 |              |                                                                                                     | VOUTA_8<br>VOUTA_9    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         | 0   | 0           | 0           | 1          | 0.5)/ 140.75)/                            |

| HZ                |              | Group A 13-bit V                                                                                    | VOUTA_10              | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         | 0   | 0           | 1           | 0          | -3.5V to +13.75V<br>(16.75V Max Swing)    |

|                   | l l          |                                                                                                     | VOUTA_11              | Х           | Χ           | Х      | Χ           | Х           | Х                    | Χ           | Х           | Х           | Х      | 0               | 0        | 1        | 0         | 0   | 0           | 1           | 1          |                                           |

|                   |              | Reserved                                                                                            | N/A                   | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         |     |             | - 01        |            | N/A                                       |

|                   |              | Group B 13-bit V                                                                                    | VOUTB_4<br>VOUTB 5    | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         | 0   | 1           | 1           | 1          | -3.5V to +13.75V<br>(16.75V Max Swing)    |

|                   | L 2          |                                                                                                     | VOUTC_4, IOUTC_4      | Х           | Х           | Х      | Х           | X           | X                    | X           | X           | Х           | Х      | 0               | 0        | 1        | 0         | 1   | 0           | 0           | 0          | V: -3.5V to +13.75V                       |

|                   | CHANNEL      | Group C 13-bit V/I                                                                                  | VOUTC_5, IOUTC_5      | Х           | Х           | х      | Х           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 1        | 0         | 1   | 0           | 0           | 1          | (16.75V Max Swing)                        |

|                   | ¥            |                                                                                                     |                       |             |             |        |             |             |                      |             |             |             |        |                 |          |          |           | Ĺ   |             |             |            | I: 0.5mA to 2.05mA                        |

|                   | ਠ            | Group D 6-bit I (Note 1)                                                                            | IOUTD_4<br>IOUTD_5    | X           | X           | X      | X           | X<br>X      | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         | 1   | 0           | 1           | 1          | 0.8mA to 1.6mA                            |

|                   | l            | PINCAST Register 2                                                                                  | N/A                   | Х           | Х           | Х      | Х           | X           | X                    | Х           | X           | Х           | X      | 0               | 0        | 1        | 0         | 1   | 1           | 0           | 0          | N/A                                       |

|                   | Į.           | Reserved                                                                                            | N/A                   | Х           | X           | Х      | Х           | Х           | Х                    | Х           | Х           | X           | Х      | 0               | 0        | 1        | 0         | 1   | 1           | 0           | 1          | N/A                                       |

|                   | }            | Select Rank 1 Calibration Registers Select Rank 2 Calibration Registers                             | 1                     | 0           | 0           | 0      | X           | X           | X                    | X           | X           | X           | 1      | 0               | 0        | 1        | 0         | 1   | 1           | 0           | 1          |                                           |

|                   | ŀ            | Configure Group C DACs as Vout                                                                      | N/A                   | 0           | 0           | 0      | X           | X           | X                    | X           | X           | 0           | X      | 0               | 0        | 1        | 0         | 1   | 1           | 0           | 1          | N/A                                       |

|                   | [            | Configure Group C DACs as lout                                                                      |                       | 0           |             | 0      | Х           |             | Х                    | Χ           | Χ           |             | Х      | 0               | 0        | 1        | 0         |     | _           |             | 0          |                                           |

|                   |              | Reserved                                                                                            | N/A                   | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 0         | 1   | 1           | 1           | 1          | N/A                                       |

|                   |              |                                                                                                     | VOUTA_12<br>VOUTA_13  | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 1         | 0   | 0           |             | 1          | -3.5V to +13.75V                          |

|                   |              | Group A 13-bit V                                                                                    | VOUTA_13<br>VOUTA_14  | Х           | Х           | Χ      | X           | X           | X                    | Х           | Χ           | Χ           | Х      | 0               | 0        | 1        | 1         | 0   | 0           |             |            | (16.75V Max Swing)                        |

|                   | ļ            |                                                                                                     | VOUTA_15              | Х           | Х           | Х      | Х           | X           | X                    | Х           | Х           |             |        | 0               | 0        | 1        | 1         | 0   |             | 1           | 1          | N/                                        |

|                   | ŀ            | Reserved                                                                                            | N/A<br>VOUTB_6        | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 1         | 0   |             | - 01<br>1   |            | N/A                                       |

|                   | က            | Group B 13-bit V                                                                                    | VOUTB_7               | X           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 1         | 0   | 1           | 1           | 1          | -3.5V to +13.75V<br>(16.75V Max Swing)    |

|                   |              |                                                                                                     | VOUTC_6, IOUTC_6      |             | X           | X      | Х           | X           | X                    | Х           | X           | Х           | Х      | 0               | 0        | 1        | 1         | 1   | -           |             | _          | V: -3.5V to +13.75V                       |

|                   | CHANNEL      | Group C 13-bit V/I                                                                                  | VOUTC_7, IOUTC_7      |             | Х           | Х      | Х           | Х           | Х                    | Х           | Х           | Х           | Х      | 0               | 0        | 1        | 1         | 1   | 0           | 0           | 1          | (16.75V Max Swing)                        |

|                   | -2           |                                                                                                     | IOUTD_6               |             |             |        |             |             |                      |             |             |             |        |                 |          |          |           |     |             |             |            | I: 0.5mA to 2.05mA                        |

|                   | ರ            |                                                                                                     | 100106                | Χ           | X           | X      | X           | X           | X                    | X           | X           | X           | X      | 0               | 0        | 1        | 1         | 1   | 0           | 1           | 1          | 0.8mA to 1.6mA                            |

|                   | ರ            | Group D 6-bit I (Note 1)                                                                            |                       | X           |             | . ^    |             |             |                      | X           | X           | X           |        | 0               |          | H        | 1         |     |             | _           |            | N/A                                       |

|                   | δ            | Group D 6-bit I (Note 1) PINCAST Register 3                                                         | IOUTD_7<br>N/A        | X           | Х           | Х      | Х           | X           | X                    |             |             |             | Х      | ٥               | 0        | 1        |           | 1   | 1           | 0           | 0          | N/A                                       |

|                   | ರ            | PINCAST Register 3 Reserved                                                                         | IOUTD_7               | X           | X           | Χ      | Χ           | Χ           | Χ                    | Χ           | Χ           | Χ           | Х      | 0               | 0        | 1        | 1         | 1   | 1           | 0           | 1          | N/A<br>N/A                                |

|                   | Ċ            | PINCAST Register 3  Reserved  Select Rank 1 Calibration Registers                                   | IOUTD_7<br>N/A<br>N/A | X<br>X<br>0 | X<br>X<br>0 | X<br>0 | X           | X<br>X      | X<br>X               | X           | X           | X           | X<br>0 | 0               | 0        | 1        | 1         | 1   | 1           | 0           | 1          | N/A                                       |

|                   | ٥<br>ا       | PINCAST Register 3 Reserved                                                                         | IOUTD_7<br>N/A        | X           | X           | Χ      | Χ           | Χ           | Χ                    | Χ           | Χ           | X<br>X<br>X | Х      | 0               | 0        | 1        | 1         | 1   | 1<br>1<br>1 | 0 0         | 1          |                                           |

|                   | δ ·          | PINCAST Register 3 Reserved Select Rank 1 Calibration Registers Select Rank 2 Calibration Registers | IOUTD_7<br>N/A<br>N/A | X<br>X<br>0 | X<br>X<br>0 | 0<br>0 | X<br>X<br>X | X<br>X<br>X | X<br>X<br>X          | X<br>X<br>X | X<br>X<br>X | X<br>X<br>X | 0<br>1 | 0 0             | 0 0      | 1 1 1    | 1 1 1     | 1 1 | 1<br>1<br>1 | 0<br>0<br>0 | 1 1 1      | N/A                                       |

Note 1: All 6-bit DACs are programmed with the MSB at the D12 bit position and extending down to D7 for the LSB. D[6:0] bit positions are "don't cares".

Table 3. Address Map (4 Channel Format)

|                       |              | Bit #                                                                                                                                          |                                                                                            | 23      | 22   | 21  | 20       | 19-16         | 15-12         | 11 | 10      | 9       | 8       | 7   | 6       | 5       | 4       | 3   | 2    | 1        | 0   |

|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|------|-----|----------|---------------|---------------|----|---------|---------|---------|-----|---------|---------|---------|-----|------|----------|-----|

|                       |              | Hex Multip                                                                                                                                     |                                                                                            |         |      | 000 |          | 0x01 0000     | 0x1000        |    |         | 100     |         |     | _       | 010     |         |     |      | 001      |     |

| FC                    | DRMAT = 0    | Binary Pos                                                                                                                                     |                                                                                            | 8       |      | _   | 1        | 8 - 1         | 8 - 1         | 8  | 4       | 2       | 1       | 8   | . 4     | 2       | 1       | 8   | 4    | 2        | 1   |

|                       |              | Item                                                                                                                                           | DAC Output<br>Pin Name                                                                     | _       | gist |     | D44      | D44 D0        | Data<br>D7 D4 | Do | DO      | D4      | Б0      | Mo  | _       | _       | annel   | 4.0 |      | Iress    | _   |

| _                     | All DACs     | Parallel Load of All DACs                                                                                                                      | All DAC Output Pins                                                                        | K2<br>X | _    | X   | راط<br>X | D11 - D8<br>X | D7 - D4<br>X  | D3 | D2<br>X | D1<br>X | D0<br>X | M1  | M0<br>0 | C1<br>0 | C0<br>0 | A3  | A2   | A 1<br>0 | A 0 |

|                       |              | Parallel Load of denoted<br>VOUTA DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0                                   | VOUTA_0 VOUTA_4 VOUTA_8 VOUTA_12                                                           | X       |      |     | X        | X             | X             | X  | X       | X       | X       | PS0 |         | PS2     |         | 0   | 0    | 0        | 0   |

|                       | GROUP A DACS | bits (PS0 is LSB).  Parallel Load of denoted  VOUTA DACs assigned to the  PINCAST "Set" addressed  using the PS2, PS1, PS0  bits (PS0 is LSB). | VOUTA_1<br>VOUTA_5<br>VOUTA_9<br>VOUTA_13                                                  | X       | х    | х   | x        | Х             | Х             | х  | Х       | х       | х       | PS0 | 1       | PS2     | PS1     | 0   | 0    | 0        | 1   |

|                       |              | Parallel Load of denoted<br>VOUTA DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | VOUTA_2<br>VOUTA_6<br>VOUTA_10<br>VOUTA_14                                                 | х       | x    | х   | х        | х             | х             | х  | х       | х       | х       | PS0 | 1       | PS2     | PS1     | 0   | 0    | 1        | 0   |

|                       |              | Parallel Load of denoted<br>VOUTA DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | VOUTA_3<br>VOUTA_7<br>VOUTA_11<br>VOUTA_15                                                 | х       | х    | х   | х        | Х             | Х             | х  | х       | х       | х       | PS0 | 1       | PS2     | PS1     | 0   | 0    | 1        | 1   |

| SN                    |              | Reserved                                                                                                                                       | N/A                                                                                        | Х       | Х    | Х   | Χ        | Χ             | Х             | Χ  | Χ       | Х       | Χ       | Χ   | Χ       | Χ       | Х       |     | 0100 | - 010    | )1  |

| PINCAST SET FUNCTIONS | P B DACs     | Parallel Load of denoted<br>VOUTB DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | VOUTB_0<br>VOUTB_2<br>VOUTB_4<br>VOUTB_6                                                   | x       | х    | х   | x        | х             | Х             | х  | Х       | х       | х       | PS0 | 1       | PS2     | PS1     | 0   | 1    | 1        | 0   |

| PINCAS                | GROUP        | Parallel Load of denoted<br>VOUTB DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | VOUTB_1<br>VOUTB_3<br>VOUTB_5<br>VOUTB_7                                                   | x       | x    | х   | х        | Х             | Х             | х  | Х       | х       | х       | PS0 | 1       | PS2     | PS1     | 0   | 1    | 1        | 1   |

|                       | GROUP C DACs | Parallel Load of denoted<br>VOUTC or IOUTC DACs<br>assigned to the PINCAST<br>"Set" addressed using the<br>PS2, PS1, PS0 bits (PS0 is<br>LSB). | VOUTC_0<br>VOUTC_2<br>VOUTC_4<br>VOUTC_6<br>or<br>IOUTC_0<br>IOUTC_2<br>IOUTC_4<br>IOUTC_6 | х       | х    | х   | х        | x             | х             | х  | х       | х       | х       | PS0 | 1       | PS2     | PS1     | 1   | 0    | 0        | 0   |

|                       | GROUP        | Parallel Load of denoted<br>VOUTC or IOUTC DACs<br>assigned to the PINCAST<br>"Set" addressed using the<br>PS2, PS1, PS0 bits (PS0 is<br>LSB). | VOUTC_1<br>VOUTC_3<br>VOUTC_5<br>VOUTC_7<br>or<br>IOUTC_1<br>IOUTC_3<br>IOUTC_5<br>IOUTC_7 | х       | х    | х   | х        | х             | х             | х  | х       | х       | х       | PS0 | 1       | PS2     | PS1     | 1   | 0    | 0        | 1   |

|                       | GROUP D DACs | Parallel Load of denoted<br>IOUTD DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | IOUTD_0<br>IOUTD_2<br>IOUTD_4<br>IOUTD_6                                                   | х       | x    | х   | х        | Х             | Х             | х  | Х       | х       | х       | PS0 | 1       | PS2     | PS1     | 1   | 0    | 1        | 0   |

|                       | GROL         | Parallel Load of denoted<br>IOUTD DACs assigned to the<br>PINCAST "Set" addressed<br>using the PS2, PS1, PS0<br>bits (PS0 is LSB).             | IOUTD_1<br>IOUTD_3<br>IOUTD_5<br>IOUTD_7                                                   | x       | x    | х   | x        | Х             | Х             | х  | Х       | х       | х       | PS0 | 1       | PS2     | PS1     | 1   | 0    | 1        | 1   |

|                       |              | Reserved                                                                                                                                       | N/A                                                                                        | Х       | Х    | Χ   | Х        | X             | Х             | Χ  | Х       | Х       | Χ       | Χ   | Χ       | Х       | Χ       |     | 1100 | -111     | 1   |

Table 3. Address Map (4 Channel Format) - cont'd

# Circuit Description (continued)

|                                     |           | Bit #                                                                   |                    | 23   | 22   | 21 | 20  | 19-16     | 15-12   | 11 | 10  | 9        | 8  | 7  | 6  | 5   | 4    | 3  | 2        | 1     | 0        |                                                                              |

|-------------------------------------|-----------|-------------------------------------------------------------------------|--------------------|------|------|----|-----|-----------|---------|----|-----|----------|----|----|----|-----|------|----|----------|-------|----------|------------------------------------------------------------------------------|

|                                     |           | Hex Multiplier                                                          |                    | _    | 0x10 |    |     | 0x01 0000 | 0x1000  |    | 0x0 |          | Ū  | Ė  |    | 010 | _    | Ů  |          | 0001  | Ů        |                                                                              |

| FORM                                | AT = 1    | Binary Position                                                         |                    | 8    | 4    | 2  | 1   | 8 - 1     | 8 - 1   | 8  | 4   | 2        | 1  | 8  | 4  | 2   | 1    | 8  | 4        | 2     | 1        | Max Output Range                                                             |

|                                     |           |                                                                         | DAC Output         | Regi | ster | •  |     |           | Data    | •  | •   | <u>'</u> |    | Мо | de | Cha | nnel |    | Add      | ress  | •        |                                                                              |

|                                     |           | Item                                                                    | Pin Name           | R2   | R1   | R0 | D12 | D11 - D8  | D7 - D4 | D3 | D2  | D1       | D0 | M1 | M0 | C1  | C0   | А3 | Α2       | A 1   | Α0       |                                                                              |

|                                     |           | Group A 13-bit V                                                        | VOUTA_0            | Х    | Χ    | Х  | Х   | Х         | Х       | Χ  | Χ   | Χ        | Χ  | 0  | 0  | 0   | 0    | 0  | 0        | 0     | 0        | -3.5V to +13.75V                                                             |

|                                     |           | Gloup A 13-bit V                                                        | VOUTA_2            | Χ    | Χ    | Х  | Χ   | Х         | Х       | Χ  | Χ   | Χ        | Χ  | 0  | 0  | 0   | 0    | 0  | 0        | 1     | 0        | (16.75V Max Swing)                                                           |

|                                     |           | Reserved                                                                | N/A                | Χ    | Χ    | Χ  | Χ   | X         | X       | Χ  | Χ   | Χ        | Χ  | 0  | 0  | 0   | 0    | 0  | 1        | 0     | 0        | N/A                                                                          |

|                                     |           | Group B 13-bit V                                                        | VOUTB_0            | Х    | Х    | Х  | Х   | Х         | Х       | Х  | Х   | Х        | Х  | 0  | 0  | 0   | 0    | 0  | 1        | 1     | 0        | -3.5V to +13.75V                                                             |

|                                     | CHANNEL 0 | Group C 13-bit V/I                                                      | VOUTC_0, IOUTC_0   | х    | х    | х  | Х   | х         | Х       | Х  | Х   | Х        | Х  | 0  | 0  | 0   | 0    | 1  | 0        | 0     | 0        | (16.75V Max Swing) V: -3.5V to +13.75V (16.75V Max Swing) I: 0.5mA to 2.05mA |

|                                     | O         | Group D 6-bit I (Note 1)                                                | IOUTD_0            | Х    | X    | X  | Х   | X         | X       | X  | Х   | X        | X  | 0  | 0  | 0   | 0    | 1  | 0        | 1     | 0        | 0.8mA to 1.6mA                                                               |

|                                     |           | PINCAST Register 0                                                      | N/A                | X    | Х    | X  | X   | X         | X       | X  | X   | X        | X  | 0  | 0  | 0   | 0    | 1  | 1        | 0     | 0        | N/A                                                                          |

|                                     |           | Select Rank 1 Calibration Registers Select Rank 2 Calibration Registers |                    | 0    | 0    | 0  | X   | X         | X       | X  | X   | X        | 1  | 0  | 0  | 0   | 0    | 1  | 1        | 1     | 0        |                                                                              |

|                                     |           | Configure Group C DAC as Vout                                           | N/A                | 0    | 0    | 0  | X   | X         | X       | X  | X   | 0        | Х  | 0  | 0  | 0   | 0    | 1  | 1        | 1     | 0        | N/A                                                                          |

|                                     |           | Configure Group C DAC as Your                                           |                    | 0    | 0    | 0  | Х   | X         | X       | X  | X   | 1        | Х  | 0  | 0  | 0   | 0    | 1  | 1        | 1     | 0        |                                                                              |

|                                     |           |                                                                         | VOUTA 1            | Х    | Х    | Х  | Х   | X         | X       | Х  | Х   | X        | Χ  | 0  | 0  | 0   | 0    | 0  | 0        | 0     | 1        | -3.5V to +13.75V                                                             |

|                                     |           | Group A 13-bit V                                                        | VOUTA 3            | Х    | Х    | X  | Х   | X         | X       | Х  | Х   | X        | X  | 0  | 0  | 0   | 0    | 0  | 0        | 1     | 1        | (16.75V Max Swing)                                                           |

|                                     |           | Reserved                                                                | N/A                | Х    | Х    | Х  | Х   | X         | X       | Х  | Х   | Х        | Χ  | 0  | 0  | 0   | 0    | 0  | 1        | 0     | 0        | N/A                                                                          |

|                                     |           | Group B 13-bit V                                                        | VOUTB_1            | Х    | Х    | Х  | Х   | Х         | Х       | Х  | Х   | Х        | Х  | 0  | 0  | 0   | 0    | 0  | 1        | 1     | 1        | -3.5V to +13.75V                                                             |

|                                     | .1        | Gloup B 10-bit V                                                        | VOOTB_1            |      | ^    | ^  |     | Α         | ^       | ^  | ۸   |          |    |    | 0  |     |      |    |          | (16.7 |          | (16.75V Max Swing) V: -3.5V to +13.75V                                       |

| 3)                                  | CHANNEL 1 | Group C 13-bit V/I                                                      | VOUTC_1, IOUTC_1   | Х    | Х    | Х  | Х   | Х         | Х       | Х  | Х   | Х        | Х  | 0  | 0  | 0   | 0    | 1  | 0        | 0     | 1        | (16.75V Max Swing)<br>I: 0.5mA to 2.05mA                                     |

| 0 tc                                | C         | Group D 6-bit I (Note 1)                                                | IOUTD_1            | Х    | Х    | Х  | Х   | X         | X       | Х  | Х   | Х        | Х  | 0  | 0  | 0   | 0    | 1  | 0        | 1     | 1        | 0.8mA to 1.6mA                                                               |

| S (                                 |           | PINCAST Register 0                                                      | N/A                | X    | X    | X  | Х   | X         | X       | X  | X   | X        | X  | 0  | 0  | 0   | 0    | 1  | 1        | 0     | 1        | N/A                                                                          |

| nn6                                 |           | Select Rank 1 Calibration Registers                                     |                    | 0    | 0    | 0  | X   | X         | X       | X  | X   | X        | 1  | 0  | 0  | 0   | 0    | 1  | 1        | 1     | 1        |                                                                              |

| Sha                                 |           | Select Rank 2 Calibration Registers  Configure Group C DAC as Vout      | N/A                | 0    | 0    | 0  | X   | X         | X       | X  | X   | 0<br>0   | X  | 0  | 0  | 0   | 0    | 1  | 1        | 1     | 1        | N/A                                                                          |